# PSA-CT4P

# **PSE Conformance Test Suite**

for 4-Pair 802.3bt PSE's

### **Product Overview**

# **Key Features**

|  | Robust 802.3bt 4-Pair PSE Conformance | Testing |

|--|---------------------------------------|---------|

|--|---------------------------------------|---------|

- ☐ Fully Automated Port Sequencing and Statistics covering up to 24 PSE Ports with one PSA-3000

- ☐ Greater than 92% 802.3bt PICS Coverage from 24 Tests Producing up to 344 Test Parameters per Port

- ☐ Fully Emulates All Type-1, 2, 3, and 4 PD's Including Single and Dual Signature Classes and PoE LLDP\*-Capable PD's

- ☐ Test Type-3 and Type-4 PSE's that Allocate Power Using Multi-Event Classification with LLDP\* Refinement

- Automatically Adapts to All Prevalent PSE Signaling and Power Management Behaviors

- ☐ Configurable Waveform Trace Diagnostic Generation and Retention

- □ Colorful and Informative Spreadsheet Reporting\*\* with Compliance (Pass/Fail) Notations and Parameter Statistics

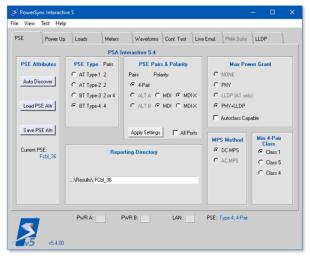

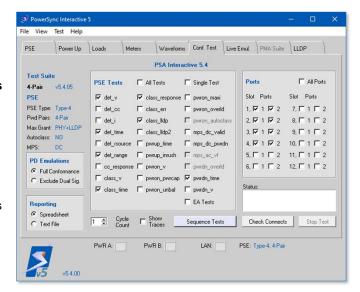

- Run & Sequence from PSA Interactive GUI or PowerShell PSA Command Line

# IEEE 802.3 PSE's

4-Pair End Span PSE's 4-Pair Mid-Span PSE's 4-Pair Power Injectors

# The Industry "Norm"

Unmatched 802.3bt Specification Coverage Widely Used by PSE Silicon Manufacturers Supports EA Gen2 PoE Logo Certification

# Fully Automated One-Button Testing

Automatic Adaptation to PSE Probing and PD Qualification Methods Flexibly Sequence Tests and Test Ports Pop-Up Spreadsheet Reporting with Statistics and Limit Evaluation

# Always Up-To-Date

Constantly Enhanced and Improved Tracking Service Support Agreement Responsive Technical Support

### Overview

With the introduction of the IEEE 802.3bt standard, Power-over-Ethernet expanded from a 30W powering system to a 90W powering system that utilizes all four wire pairs within Cat 5/6/7 cabling. In order to facilitate this change, extensive new features were added placing many new demands on both power sourcing equipment (PSE's) and powered devices (PD's). On the PSE side, the added complexity is perhaps best demonstrated by the IEEE 802.3 state machine growth from 4 pages in 802.3at to 31 pages in802.3bt.

### Higher Power, Higher Flexibility with 802.3bt

Before 802.3bt, PD's were restricted to receiving power on two wire pairs with a maximum load at the PD interface of 25.5 watts. With 802.3bt, PD's can be designed to draw over 70 watts from four wire pairs and further, PD's may choose to combine that power to one integrated power load or to split it into two autonomous power loads. PSE's are challenged to recognize 13 different classes of PD's and power those classes appropriately while also overcoming imperfections in cabling and components that cause 4-pair power to divide unevenly between wire pairs. While 802.3at introduced one mode of PD power demotion, 802.3bt introduces 27 possible scenarios whereby PD's are granted less power than requested.

The 802.3bt standard also specifies an enhanced PoE Link Layer Discovery Protocol (LLDP) that includes a number of new TLV's while maintaining PD power allocations with a granularity of 0.1 watt.

### **Fully Automated Testing with Very High Test Coverage**

Given the complexity of a fully compliant 4-Pair 802.3bt PSE, the range of test cases that must be run is so enormous as to prohibit manual testing as a practical solution. The 4-Pair PSE Conformance Test Suite produces over 300 test parameters for each PSE port tested with a maximum possible count of 352 test parameters. The test suite automatically adapts to a wide range of possible PSE implementations and produces a number of implementation-specific test parameters.

The 25 tests that make up the 4-Pair Conformance

Test Suite cover **92% of the PSE PICS** in the IEEE

802.3bt including those individual PICS that cover

dozens of technical specifications. The 4-Pair PSE

Conformance Test Suite is widely used throughout the internetworking community as the industry "norm" for PSE specification compliance.

Combined with the PowerSync Analyzer, the 4-Pair PSE Conformance Test Suite is qualified for Ethernet Alliance **Gen2 PoE Logo**Certification testing enabling manufacturers to perform the testing required for EA PoE Logo marks in-house.

### IEEE 802.3af, 802.3at, 802.3bt Cross-Compatibility

All 802.3bt PSE's must properly recognize and power PD's developed under the 802.3af, 802.3at, and 802.3bt standards. The 4-Pair PSE Conformance Test Suite includes emulations of many PD's including those conforming to the older standards.

### **Robust Diagnostics and Reporting**

The 4-Pair PSE Conformance Test Suite automatically sequences to a pop-up spreadsheet report with full color notations of parameter pass/fail state per port and cross-port statistics for each parameter. Also included are Sifos proprietary scores for PSE Safety and PSE Interoperability.

<sup>\*</sup> LLDP Emulation & Analysis feature license is sold separately.

<sup>\*\*</sup> Microsoft Excel 2007 or later required

### **PSE Conformance Tests & Parameters**

### **Detection & Connection Check Probing and Functional Tests**

### det\_v Detection Probe Physical Parameters

Captures and analyzes PSE detection probe voltages with both valid and slightly non-valid detection signatures emulating single and dual signature PD's.

Open\_Circuit\_Voc\_APeak Open Circuit Detection Voltage on Alt-A PairsetOpen\_Circuit\_Voc\_BPeak Open Circuit Detection Voltage on Alt-B Pairset

Backoff\_Voltage\_A

IDLE State voltage during detection backoff on the Alt-A Pairset

IDLE State voltage during detection backoff on the Alt-A Pairset

Backoff\_Voltage\_Ss

IDLE State voltage during Single Signature detection backoff across both Pairsets (as a single

signature PD would detect it)

Max\_Det\_Step\_V\_AMaximum Detection Voltage with Valid Detection Signature - Alt-A PairsetMax\_Det\_Step\_V\_BMaximum Detection Voltage with Valid Detection Signature - Alt-B PairsetMin\_Det\_Step\_V\_BMinimum Valid Step Voltage with Valid Detection Signature - Alt-B PairsetMin\_Det\_Step\_V\_BMinimum Valid Step Voltage with Valid Detection Signature - Alt-B Pairset

Det\_Step\_Changes\_A Count of Detection Step Transitions on the Alt-A Pairset

Det\_Step\_Changes\_B Count of Detection Step Transitions on the Alt-B Pairset

Min\_Step\_DV\_A

Detection Step Magnitude from Max Voltage to Min Voltage - Alt-A Pairset

Min\_Step\_DV\_B

Detection Step Magnitude from Max Voltage to Min Voltage - Alt-A Pairset

Pre-Det\_CC\_Step\_V\_A

Magnitude of any non-802 pre-detection signaling on the Alt-A Pairset

Magnitude of any non-802 pre-detection signaling on the Alt-A Pairset

### det cc Connection Check Probe Physical Parameters

Captures and analyzes PSE 4-pair connection check probe voltages with both valid and slightly non-valid detection signatures emulating single and dual signature PD's.

**Presumed\_CC\_DET\_SEQ** CC\_DET\_SEQ as described by the 802.3bt PSE State Machine, derived from observations of signaling at the PSE physical interface.

Conn\_Chk\_SS\_V\_APeak connection check voltage on the Alt-A Pairset with Single SignatureConn\_Chk\_SS\_V\_BPeak connection check voltage on the Alt-B Pairset with Single SignatureConn\_Chk\_DS\_V\_APeak connection check voltage on the Alt-A Pairset with Dual SignatureConn\_Chk\_DS\_V\_BPeak connection check voltage on the Alt-B Pairset with Dual Signature

High\_Signature\_CC\_A

Flag indicating invalid signature compliance to PSE state machine on the Alt-A Pairset. 1 is a

PASS, 0 is a FAIL.

High\_Signature\_CC\_B Flag indicating invalid signature compliance to PSE state machine on the Alt-B Pairset. 1 is a

PASS, 0 is a FAIL

4Pair\_Start\_Fail Flag indication that the 4-Pair PSE failed to produce any signaling on at least one Pairset when a

valid PD signature was connected.

### det\_i Detection Current Limiting and Slew Rate

Measures maximum current sourcing capability from a PSE during detection. This behavior is essential to protecting non-PD's connected to the PSE.

Isc\_Init\_APeak detection current @ >1.5V on the Alt-A PairsetIsc\_Init\_BPeak detection current @ >1.5V on the Alt-B PairsetIsc\_Det\_APeak detection current @ >2.2V on the Alt-A PairsetIsc\_Det\_BPeak detection current @ >2.2V on the Alt-B Pairset

Det\_Slew\_A

Maximum expected detection voltage slew rate on the Alt-A Pairset

Det\_Slew\_B

Maximum expected detection voltage slew rate on the Alt-B Pairset

### det time Detection & Connection Check Timing

Measures detection backoff and detection / connection check probe timing parameters.

Detect\_Time\_Tdet\_A

Time from start of detection until end of detection on the Alt-A Pairset

Detect\_Time\_Tdet\_B

Time from start of detection until end of detection on the Alt-A Pairset

### **Detection & Connection Check Probing and Functional Tests**

(IDLE state) Time from end of a detection sequence until start of a new detection sequence given **Backoff Time SS**

an invalid Single Signature

CC DET SEQ 0, 1, and 3 ONLY: The time duration between the end of detection on the PRI Det2Det\_Time

Pairset and the start of detection on the SEC pairset.

CC DET SEQ 2 ONLY: The total time duration of Detection on both pairsets and Connection Det+CC Time

Check.

CC2Det\_Time CC\_DET\_SEQ 0, 3 ONLY: The time from end of Connection Check until start of the first Pairset

Detection.

#### det rsource **Detection Source Impedance**

Determine the type of detection probe (voltage versus current probing) and determine effective source impedance of a current probing scheme. Assesses risk of PSE port powering another PSE port.

PSE\_Detect\_Source PSE Detection Scheme. 0= Voltage probing, 1= Current probing.

The source impedance of the Detection probing on the Alt-A Pairset. A pure voltage source will PSE\_Source\_Zout\_A

report as  $0 \Omega$ .

**PSE Source Zout B** The source impedance of the Detection probing on the Alt-B Pairset. A pure voltage source will

report as  $0 \Omega$ .

#### det\_range **Detection Accept and Reject Ranges**

Assesses the range of acceptable PD signatures given both single and dual signature PD emulations.

Rgood\_Max\_Single Maximum Detection signature resistance that gets powered given a Single Signature PD Minimum Detection signature resistance that gets powered given a Single Signature PD Rgood\_Min\_Single

Cgood\_Max\_Single Maximum Capacitive signature that gets powered given a Single Signature PD

Maximum Detection signature resistance that gets powered on the Alt-A Pairset given a Dual Rgood\_Max\_Dual\_A

Signature PD

Maximum Detection signature resistance that gets powered on the Alt-B Pairset given a Dual Rgood\_Max\_Dual\_B

Signature PD

Minimum Detection signature resistance that gets powered on the Alt-A Pairset given a Dual Rgood Min Dual A

Signature PD

Minimum Detection signature resistance that gets powered on the Alt-B Pairset given a Dual Rgood\_Min\_Dual\_B

Signature PD

Cgood\_Max\_Dual\_A Maximum Capacitive signature that gets powered on the Alt-A Pairset given a Dual Signature PD

Cgood Max Dual B Maximum Capacitive signature that gets powered on the Alt-B Pairset given a Dual Signature PD

#### cc response Connection Check Validity

Determines that connection check performed by a 4-pair PSE properly resolves single versus dual signature PD implementations. Also assesses PSE response to a 2-pair PD connection.

Flag indicating that the PSE properly characterized a Single Signature PD prior to powering. 1= Single\_Sig\_Response

Success, 0= Failure.

Flag indicating that the PSE properly characterized a Dual Signature PD prior to powering. 1= Dual\_Sig\_Response

Success, 0= Failure.

Flag indicating the count of Pairsets powered when a valid PD signature is connected only on the 2Pair\_PD\_A

Alt-A Pairset. 0= No Pairsets powered, 1= Alt-A Pairset powered, 2= both pairsets powered.

Flag indicating the count of Pairsets powered when a valid PD signature is connected only on the 2Pair\_PD\_B Alt-B Pairset. 0= No Pairsets powered, 1= Alt-A Pairset powered, 2= both pairsets powered.

# Classification Probing and Functional Tests

#### Classification Voltages class v

Captures and analyzes PSE classification and class probe voltage levels, focusing on only the final classification performed prior to power-up. Also analyzes class probe reset where presented.

Maximum Class Event Voltage measured as the peak of both pairsets given a Single Signature Vclass\_max\_SS

PD emulation

Minimum Class Event Voltage measured as the peak of both pairsets given a Single Signature PD Vclass min SS

Vmark\_SS Median Mark region voltage from the peak of both pairsets given a Single Signature PD emulation If the PSE utilizes a Class Probe given Single Signature PD connection, this is the maximum Vreset\_SS voltage following the completion of the class probe until the start of Event 1 Classification. Reports -1 if there is no class reset. Vclass\_max\_DSA Maximum Class Event Voltage on the Alt-A Pairset given a Dual Signature PD emulation Vclass max DSB Maximum Class Event Voltage on the Alt-B Pairset given a Dual Signature PD emulation Vclass\_min\_DSA Minimum Class Event Voltage on the Alt-A Pairset given a Dual Signature PD emulation Vclass\_min\_DSB Minimum Class Event Voltage on the Alt-B Pairset given a Dual Signature PD emulation Vmark\_DSA Median Mark region voltage on the Alt-A Pairset given a Dual Signature PD emulation Vmark DSB Median Mark region voltage on the Alt-B Pairset given a Dual Signature PD emulation If the PSE utilizes a Class Probe given Dual Signature PD connection, this is the maximum

Vreset\_DSA voltage following the completion of the class probe until the start of Event 1 Classification on the

Alt-A Pairset. Reports -1 if there is no class reset.

Vreset\_DSB If the PSE utilizes a Class Probe given Dual Signature PD connection, this is the maximum

voltage following the completion of the class probe until the start of Event 1 Classification on the

Alt-A Pairset. Reports -1 if there is no class reset.

### class time Classification Timing

Captures and analyzes PSE classification signal timing, focusing on only the final classification performed prior to power-up.

Class\_Probe\_SS

Flag indicating if a Class Probe is discovered given a Single Signature PD. 1= Class Probe

Discovered, 0= No Class Probe.

Class Event Count in response to Class 7 (Single Signature) PD on either the Alt-A or Alt-B

pairset.

Duration of Event #1 (LCE) Class Pulse prior to power-up given a Single Signature PD

Long\_EV1\_Time\_SS Connection.

Min\_Class\_EV\_Time\_SS Minimum duration of any non-LCE Class Event prior to power-up given a Single Signature PD.

Max\_Class\_EV\_Time\_SS Maximum duration of any non-LCE Class Event prior to power-up given a Single Signature PD.

Min\_Mark\_EV\_Lowl\_SS First mark event time duration given a low 0.5mA mark load from PD.

Min\_Mark\_EV\_Time\_SS Minimum duration of any non-final Mark Event prior to power-up given a Single Signature PD.

Max\_Mark\_EV\_Time\_SS Maximum duration of any non-final Mark Event prior to power-up given a Single Signature PD.

Final\_Mark\_EV\_Time\_SS Duration of the final Mark Event leading into Power-Up given a Single Signature PD.

If the PSE utilizes a Class Probe given Single Signature PD connection, this is the time duration

CI\_Prb\_Reset\_Time\_SS

If the PSE utilizes a class Probe given Single signature PD connection, this is the time duration from end-of-Class-Probe until start of Event #1. Set to -1 if no class probing.

Class\_Probe\_DA Flag indicating if a Class Probe is discovered on the Alt-A Pairset given a Dual Signature PD. 1= Class Probe Discovered, 0= No Class Probe.

**EV\_Count\_5D\_DA** Class Event Count on the Alt-A Pairset in response to a Dual Class 5 PD

**Long\_EV1\_Time\_DA**Duration of Event #1 (LCE) Class Pulse prior to power-up on the Alt-A Pairset given a Dual Signature PD connection.

Min\_Class\_EV\_Time\_DA Minimum duration of any non-LCE Class Event on the Alt-A Pairset prior to power-up given a Dual Signature PD.

Min\_Mark\_EV\_Time\_DA Minimum duration of any non-final Mark Event on the Alt-A Pairset prior to power-up given a Dual Signature PD.

Max\_Mark\_EV\_Time\_DA Maximum duration of any non-final Mark Event on the Alt-A Pairset prior to power-up given a Dual Signature PD.

Final\_Mark\_EV\_Time\_DA Duration of the final Mark Event on the Alt-A Pairset leading into Power-Up given a Dual Signature PD.

Cl\_Prb\_Reset\_Time\_DA

If the PSE utilizes a Class Probe on the Alt-A Pairset given a Dual Signature PD connection, this is the time duration from end-of-Class-Probe until start of Event #1. Set to -1 if no class probing.

Class\_Probe\_DB Flag indicating if a Class Probe is discovered on the Alt-B Pairset given a Dual Signature PD. 1= Class Probe Discovered, 0= No Class Probe.

EV\_Count\_5D\_DB Class Event Count on the Alt-B Pairset in response to a Dual Class 5 PD

**Long\_EV1\_Time\_DB**Duration of Event #1 (LCE) Class Pulse prior to power-up on the Alt-B Pairset given a Dual Signature PD connection.

Min\_Class\_EV\_Time\_DB Minimum duration of any non-LCE Class Event on the Alt-B Pairset prior to power-up given a Dual Signature PD.

Maximum duration of any non-LCE Class Event on the Alt-B Pairset prior to power-up given a Max\_Class\_EV\_Time\_DB

Dual Signature PD.

Minimum duration of any non-final Mark Event on the Alt-B Pairset prior to power-up given a Dual Min\_Mark\_EV\_Time\_DB

Signature PD.

Maximum duration of any non-final Mark Event on the Alt-B Pairset prior to power-up given a Dual Max\_Mark\_EV\_Time\_DB

Signature PD.

Duration of the final Mark Event on the Alt-B Pairset leading into Power-Up given a Dual Signature Final\_Mark\_EV\_Time\_DB

CI\_Prb\_Reset\_Time\_DB If the PSE utilizes a Class Probe on the Alt-B Pairset given a Dual Signature PD connection, this

is the time duration from end-of-Class-Probe until start of Event #1. Set to -1 if no class probing.

#### class response

### **PSE Classification Responses to All PD Types**

Evaluates PSE responses to a variety of PD types including both single and dual signature. Assesses maximum power PSE will grant at power-up and PSE 2-pair powering behavior.

Class Event count in response to Class 3 (Single Signature) PD Class\_3\_Count Class\_4\_Count Class Event count in response to Class 4 (Single Signature) PD Class Event count in response to Class 5 (Single Signature) PD Class\_5\_Count Class\_6\_Count Class Event count in response to Class 6 (Single Signature) PD Class\_7\_Count Class Event count in response to Class 7 (Single Signature) PD Class\_8\_Count Class Event count in response to Class 8 (Single Signature) PD

Class\_2D\_Count\_A Class Event count on the Alt-A Pairset in response to a Dual Class 2 PD Class\_2D\_Count\_B Class Event count on the Alt-B Pairset in response to a Dual Class 2 PD Class\_3D\_Count\_A Class Event count on the Alt-A Pairset in response to a Dual Class 3 PD Class\_3D\_Count\_B Class Event count on the Alt-B Pairset in response to a Dual Class 3 PD Class\_4D\_Count\_A Class Event count on the Alt-A Pairset in response to a Dual Class 4 PD Class 4D Count B Class Event count on the Alt-B Pairset in response to a Dual Class 4 PD Class\_5D\_Count\_A Class Event count on the Alt-A Pairset in response to a Dual Class 5 PD Class\_5D\_Count\_B Class Event count on the Alt-B Pairset in response to a Dual Class 5 PD

Max\_SS\_Class Maximum Assigned Class available to Single Signature PD's

Max\_DS\_Class Maximum Assigned Class available to both pairsets of Dual Signature PD's

Flag indicating that the maximum power granted to Dual Signature PD's corresponds to the Init\_Grant\_Match

maximum power granted to Single Signature PD's. 1= Correspondance, 0 = Inconsistent

Flag indicating which Pairset gets 2-Pair powered if and when the PSE performs 2-Pair powering. 2-Pair\_Pairset

Set to 0 if PSE always 4-Pair powers, 1 if Alt-A Pairset powered, 2 if Alt-B Pairset powered.

Primary (PRI) Pairset where Classification occurs given Single Signature PD connection. 1= Alt-A

Pairset, 2= Alt-B Pairset, 12= Either Pairset.

### class err

PRI\_4pr\_Pairset

### PSE Processing of Deviant Class Signatures

Evaluates PSE current limiting to very high class and mark loads and PSE powering response to current limited signatures and to invalid class signature sequences.

Class\_Ilim\_A Classification Event current limit on the Alt-A Pairset. Class Ilim B Classification Event current limit on the Alt-B Pairset.

Flag indicating if PSE powers a 52mA Class signature given a Single Signature PD. 0= No Power. Pwr\_Cl\_52\_SS

1= Power Applied.

Flag indicating if PSE powers the Alt-A Pairset a 52mA Class signature given a Dual Signature Pwr\_CI\_52\_DSA

PD. 0= No Power. 1= Power Applied.

Flag indicating if PSE powers the Alt-B Pairset a 52mA Class signature given a Dual Signature Pwr\_CI\_52\_DSB

PD. 0= No Power. 1= Power Applied.

Flag indicating if PSE produces at least 15msec of IDLE time and voltage on both pairsets Class Reset SS

following and aborted classification sequence with a single signature PD.

Flag indicating if PSE produces at least 15msec of IDLE time and voltage on each pairset Class\_Reset\_DS

following aborted classification sequences with a dual signature PD.

Mark\_Ilim\_A Mark Event current limit on the Alt-A Pairset. Mark Event current limit on the Alt-B Pairset. Mark\_Ilim\_B

class\_lldp

| Inval_Sig_EV2_SS  | Flag indicating if the PSE powers an uneven 2-Event classification given a Single Signature PD where Event 1 is 40mA, Event 2 is 18 mA. 0 = No Power, 1= Power Applied. =0 for 1-Event PSE.    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inval_Sig_EV4_SS  | Flag indicating if the PSE powers an uneven 4-Event classification given a Single Signature PD where Event #4 differs from Event #3. 0 = No Power, 1= Power Applied. =0 for < 4-Event PSE.     |

| Inval_Sig_EV5_SS  | Flag indicating if the PSE powers an uneven 5-Event classification given a Single Signature PD where Event #5 differs from Event #4. 0 = No Power, 1= Power Applied. =0 for < 5-Event PSE.     |

| Inval_Sig_EV2_DSA | Flag indicating if the PSE powers the Alt-A Pairset following an uneven 2-Event classification given a Dual Signature PD. 0 = No Power, 1= Power Applied.                                      |

| Inval_Sig_EV2_DSB | Flag indicating if the PSE powers the Alt-B Pairset following an uneven 2-Event classification given a Dual Signature PD. 0 = No Power, 1= Power Applied. =0 for 1-Event PSE.                  |

| Inval_Sig_EV4_DSA | Flag indicating if the PSE powers the Alt-A Pairset following an uneven 4-Event classification where Event #4 differs from Event #3 given a Dual Signature PD. 0 = No Power, 1= Power Applied. |

| Inval_Sig_EV4_DSB | Flag indicating if the PSE powers the Alt-B Pairset following an uneven 4-Event classification where Event #4 differs from Event #3 given a Dual Signature PD. 0 = No Power, 1= Power Applied. |

### **LLDP Protocol & Power Grant Testing Emulating Single Signature PD's**

|                      | (29 octet) basic protocol fields, protocol timing, and power request processing for 802.3bt single DP Emulation & Analysis feature license.)                                                                                                                                 |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSE_LLDP_Time_SS     | Time from Power On to 1st LLDP Frame1 = No Frame Received < 45 seconds                                                                                                                                                                                                       |

| LLDP_Length          | TLV Length Field. 29 for 802.3bt                                                                                                                                                                                                                                             |

| PSE_Pwr_Pair         | MDI Legacy Powered Pair. Confirm the value of either 1 or 2. All other values fail. Value = 1 means the Signal Pairs are in use.  Value = 2 means the Spare Pairs are in use.                                                                                                |

| PSE_MDI_Pwr_Sup      | MDI Power Support Field. 4 bit value where bits 0-2 are set and bit 3 is don't care.                                                                                                                                                                                         |

| PSE_Pwr_Class        | MDI 802.3at PSE Class Support. Class 4 and above will specify 4                                                                                                                                                                                                              |

| PSE_Source_Priority  | MDI 802.3at Type-Source-Priority field. If PSE is Type-3 and Type-4 it will specify Type-2                                                                                                                                                                                   |

| PSE_Ext_Type         | Extended PSE Type. Either Type-3 or Type-4                                                                                                                                                                                                                                   |

| PSE_Ext_Status_SS    | Powering Status of PSE. =41 if set to Both_Alts and 4pr_Pwr_Single =21 if et to Alt_A or Alt_B and 2pr_Pwr. Otherwise set to 0.                                                                                                                                              |

| PSE_Ext_Class_SS     | Assigned Class available from the PSE. =41 if Class between 1 and 8 and 4pr_Pwr_Single. =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0                                                                                                                         |

| PSE_Max_Pwr_SS       | Reported PSE maximum available port power. There are no restrictions on this value.                                                                                                                                                                                          |

| PSE_Class_6_Ext_Pwr  | Flag indicating that PSE allows extended power allocations to a Class 6 PD.  If PSE_Max_Pwr_SS reports > 51.0 watts, a class 6 LLDP power request exceeding 51.0 watts is performed. 0 = Power Allocation limited to 51.0 watts and 1= Power Allocation exceeded 51.0 watts. |

| PSE_Pwr_Class_DS     | Value of the Dual-sig Extended Class for Alt-A and Alt-B. Set to 1 if both TLVs are set to Single Signature otherwise set to 0.                                                                                                                                              |

| PSE_Echo_Time_1SS    | Time from a PD request for an initial power until the frame containing the Echo of that request is received                                                                                                                                                                  |

| PSE_Alloc_Time_1SS   | Time from a PD request for an initial power until the frame containing the Allocation of that request is received                                                                                                                                                            |

| PSE_Alloc_LowPwr_1SS | Power Allocated by the PSE when requesting an initial power                                                                                                                                                                                                                  |

| PSE_Echo_Time_2SS    | Time from a PD request for a change to the max power available until the frame containing the Echo of that request is received                                                                                                                                               |

| PSE_Alloc_Time_2SS   | Time from a PD request for a change to the max power available until the frame containing the Allocation of that request is received                                                                                                                                         |

| PSE_Alloc_MaxPwr_2SS | Indicates Power was Allocated by the PSE when requesting a change to the max power available. =1 if Allocated, =0 if Not Allocated                                                                                                                                           |

| PSE_AT_Pwr_Neg       | Flag indicating that PSE supports 802.3at PoE TLV's (12-octet) protocol.                                                                                                                                                                                                     |

| PSE_Post_AT_Pwr_Neg  | Flag indicating that PSE will return to 802.3bt PoE TLV's following a prior PD connection that negotiated using 802.3at PoE TLV's.                                                                                                                                           |

Link\_Down\_Shutdown

Disconnect the LAN. Set to 1 if Power NOT removed. 0 if Power removed

| Assesses 802.3bt PSE LLDP (29 octet) basic protocol fields, protocol timing, and power request processing for 802.3bt dual signature PD's. (Requires LLDP Emulation & Analysis feature license.)  PSE_LLDP_Time_DS  Time from Power On to 1st LLDP Frame1 = None Received < 45 sec.  Powering Status of PSE.  PSE_Ext_Status_DS  =42 if set to Both_Alts and 4pr_Pwr_Dual  =21 if et to Alt_A or Alt_B and 2pr_Pwr. Otherwise set to 0.  Assigned Class available from the PSE on Alt-A.  PSE_Ext_Class_DSA  =42 if Class between 1 and 5 and 4pr_Pwr_Dual.  =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Assigned Class available from the PSE on Alt-B.  PSE_Ext_Class_DSB  =42 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Assigned Class available from the PSE on Alt-B.  PSE_Max_Pwr_DS  PSE_Max_Pwr_DS  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  Time from a PD request for a change to a low power until the frame containing the Echo of that request is received  Time from a PD request for a change to a low power until the frame containing the Allocation of the parts of the state of the st    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSE_Ext_Status_DS  PSE_Ext_Status_DS  =42 if set to Both_Alts and 4pr_Pwr_Dual =21 if et to Alt_A or Alt_B and 2pr_Pwr. Otherwise set to 0.  Assigned Class available from the PSE on Alt-A.  PSE_Ext_Class_DSA  =42 if Class between 1 and 5 and 4pr_Pwr_Dual. =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Assigned Class available from the PSE on Alt-B.  PSE_Ext_Class_DSB  PSE_Ext_Class_DSB  =42 if Class between 1 and 5 and 4pr_Pwr_Dual. =21 if Class between 1 and 5 and 4pr_Pwr_Dual. =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  PSE_Pwr_Class_SS  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  Time from a PD request for a change to a low power until the frame containing the Echo of that request is received  Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ### PSE_Ext_Status_DS  ### = 42 if set to Both_Alts and 4pr_Pwr_Dual ### = 21 if et to Alt_A or Alt_B and 2pr_Pwr. Otherwise set to 0.  ### Assigned Class available from the PSE on Alt-A.  ### PSE_Ext_Class_DSA  ### PSE_Ext_Class_DSA  ### PSE_Ext_Class_DSB  ### PSE_Ext_Class_DSB  ### PSE_Ext_Class_DSB  ### PSE_Ext_Class_DSB  ### PSE_Ext_Class_DSB  ### PSE_Max_Pwr_DS  ### PSE_Max_Pwr_DS  ### PSE_Pwr_Class_SS  ### PSE_Pwr_Class_SS  ### PSE_Pwr_Class_SS  ### PSE_Ext_Class_DSB  ### PSE_Ext_Class_DSB  ### PSE_Ext_Class_DSB  ### PSE_Pwr_Class_SS  ### PSE_Pwr_Class_SS  ### PSE_Ext_Class_DSB  ### PSE_Pwr_Class_SS  ### PSE_Ext_Class_DSB  ### PSE_Pwr_Class_SS  ### PSE_Ext_Class_DSB  ### PSE |

| =21 if et to Alt_A or Alt_B and 2pr_Pwr. Otherwise set to 0.  Assigned Class available from the PSE on Alt-A.  =42 if Class between 1 and 5 and 4pr_Pwr_Dual.  =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Assigned Class available from the PSE on Alt-B.  PSE_Ext_Class_DSB  PSE_Ext_Class_DSB  =42 if Class between 1 and 5 and 4pr_Pwr_Dual.  =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  PSE_Pwr_Class_SS  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  Time from a PD request for a change to a low power until the frame containing the Echo of that request is received  Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Assigned Class available from the PSE on Alt-A.  =42 if Class between 1 and 5 and 4pr_Pwr_Dual. =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Assigned Class available from the PSE on Alt-B.  PSE_Ext_Class_DSB  =42 if Class between 1 and 5 and 4pr_Pwr_Dual. =21 if Class between 1 and 5 and 4pr_Pwr_Dual. =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  PSE_Pwr_Class_SS  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  Time from a PD request for a change to a low power until the frame containing the Echo of that request is received  Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ### PSE_Ext_Class_DSA  ### = 42 if Class between 1 and 5 and 4pr_Pwr_Dual.  ### = 21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  ### Assigned Class available from the PSE on Alt-B.  ### PSE_Ext_Class_DSB  ### PSE_Ext_Class_DSB  ### = 42 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  ### PSE_Ext_Class_DSB  ### = 42 if Class between 1 and 5 and 4pr_Pwr_Dual.  ### = 21 if Class between 1 and 5 and 4pr_Pwr_Dual.  ### = 22 if Class between 1 and 5 and 4pr_Pwr. Otherwise set to 0  ### Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  ### Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  ### PSE_Echo_Time_1DS  ### PSE_Echo_Time_1DS  ### PSE_Allea Time_1DS  ### Time from a PD request for a change to a low power until the frame containing the Allocation of the PSE_Allea Time_1DS  ### PSE_Allea Time_1DS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0 Assigned Class available from the PSE on Alt-B.  =42 if Class between 1 and 5 and 4pr_Pwr_Dual. =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  PSE_Max_Pwr_DS  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  PSE_Pwr_Class_SS  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  PSE_Echo_Time_1DS  Time from a PD request for a change to a low power until the frame containing the Echo of that request is received  Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Assigned Class available from the PSE on Alt-B.  =42 if Class between 1 and 5 and 4pr_Pwr_Dual. =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  PSE_Pwr_Class_SS  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  PSE_Echo_Time_1DS  Time from a PD request for a change to a low power until the frame containing the Echo of that request is received  Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PSE_Ext_Class_DSB =42 if Class between 1 and 5 and 4pr_Pwr_Dual. =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  PSE_Pwr_Class_SS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| =21 if Class between 1 and 4 and 2pr_Pwr. Otherwise set to 0  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  PSE_Pwr_Class_SS  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  PSE_Echo_Time_1DS  PSE_Allow Time_1DS  Time from a PD request for a change to a low power until the frame containing the Echo of that request is received  Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PSE_Max_Pwr_DS  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  PSE_Echo_Time_1DS  PSE_Allow Time_1DS  Reported PSE maximum available port power. There are no restrictions on this value. Value is the sum of both pairsets.  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  Time from a PD request for a change to a low power until the frame containing the Allocation of Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| the sum of both pairsets.  PSE_Pwr_Class_SS  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  PSE_Echo_Time_1DS  PSE_Allow Time_1DS  the sum of both pairsets.  Value of the Single-sig Extended Class for Alt-A and Alt-B. Set to 1 if TLV is set to Single Signature otherwise set to 0.  Time from a PD request for a change to a low power until the frame containing the Allocation of Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Signature otherwise set to 0.  PSE_Echo_Time_1DS  Signature otherwise set to 0.  Time from a PD request for a change to a low power until the frame containing the Echo of that request is received  Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| request is received  Time from a PD request for a change to a low power until the frame containing the Allocation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| that request is received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PSE_Alloc_LowPwr_1DSA Power Allocated on Alt-A by the PSE when requesting a change to a low power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PSE_Alloc_LowPwr_1DSB Power Allocated on Alt-B by the PSE when requesting a change to a low power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PSE_Echo_Time_2DS  Time from a PD request for a change to the max power available until the frame containing the Echo of that request is received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PSE_Alloc_Time_2DS  Time from a PD request for a change to the max power available until the frame containing the Allocation of that request is received                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PSE_Alloc_MaxPwr_2DSA Indicates Power was Allocated on Alt-A by the PSE when requesting a change to the max power available. =1 if Allocated, =0 if Not Allocated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PSE_Alloc_MaxPwr_2DSB Indicates Power was Allocated on Alt-B by the PSE when requesting a change to the max power available. =1 if Allocated, =0 if Not Allocated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PSE_Alloc_Limit_DS  Flag indicating if PSE will over-allocate to a Class 3 D power-up. 1 = max allocation consistent with assigned pairset classe. 0= allocation exceeded pairset assigned classes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## **Power-Up Processes**

| pwrup_time Po              | wer-Up Timing Parameters                                                                                                                                                                      |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Measures power-up rise tin | ne and time delay from completion of detection until POWER_ON state.                                                                                                                          |

| Pwr_On_Time_Tpon_SS        | Time duration from the end of Detection and Connection Check until the end of the POWER_UP state given a Single Signature PD.                                                                 |

| Pwr_On_Time_Tpon_DS/       | Time duration from the end of Detection and Connection Check until the end of the POWER_UP state on the Alt-A Pairset given a Dual Signature PD.                                              |

| Pwr_On_Time_Tpon_DSB       | Time duration from the end of Detection and Connection Check until the end of the POWER_UP state on the Alt-B Pairset given a Dual Signature PD.                                              |

| Pwrup_Rise_Time_A          | Estimated time ( $\mu$ sec) for the Alt-A Pairset to transit from 10% of Vpse to 90% of Vpse while applying power.                                                                            |